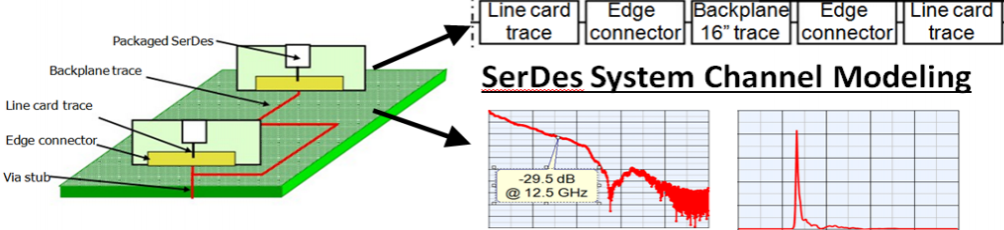

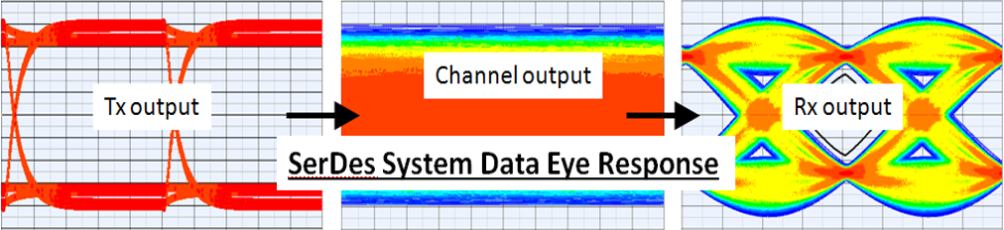

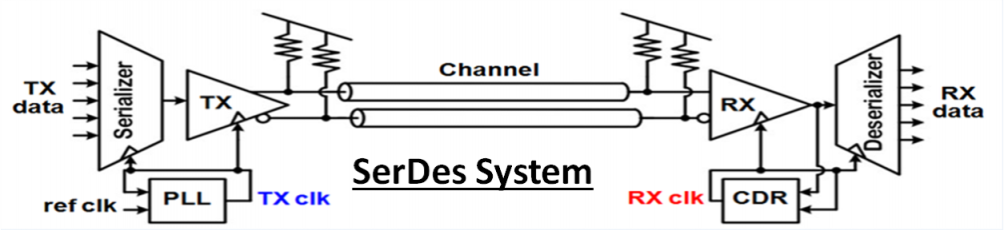

High speed digital (HSD) serial-deserializer (SerDes) system channel simulation is critical for SerDes system design and validation. The simulation must run fast while achieving adequate accuracy. Today’s SerDes system vendors require HSD IBIS-AMI (Input/Output Buffer Information – Algorithmic Modeling Interface) models long before silicon is available. To meet the demand, HSD silicon vendors desire an… Continue Reading

Tools, Technologies and Training for High Speed Digital SerDes System Designers

Monthly Archives: September 2015

Statistical Model Development for High Speed SerDes with LSI

IBIS Algorithmic Modeling Interface (IBIS-AMI) defines two approaches to SerDes modeling and simulation flow: time domain or bit-by-bit simulation for nonlinear and/or time variant (NLTV) model and statistical simulation for linear and time invariant (LTI) model. Statistical simulation has advantages of faster simulation speed and arbitrary low BER floor under linear model assumption. However, the… Continue Reading