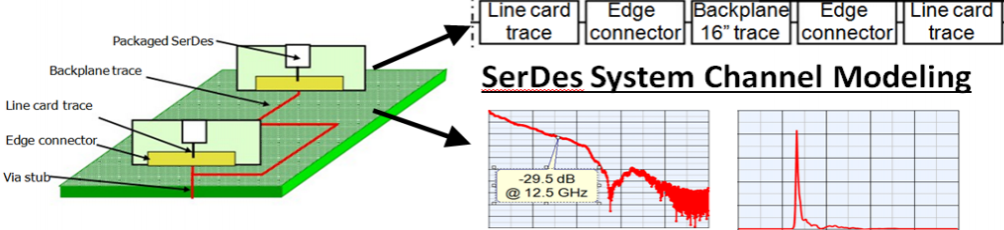

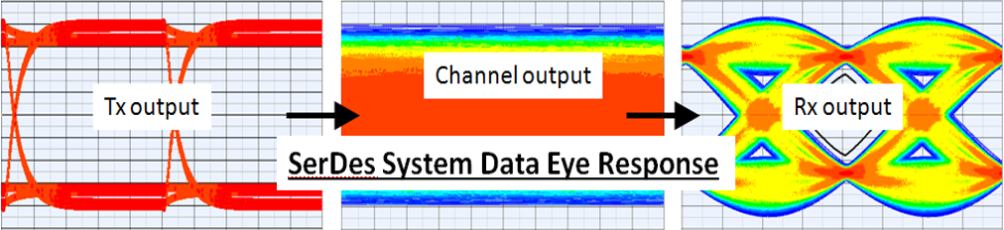

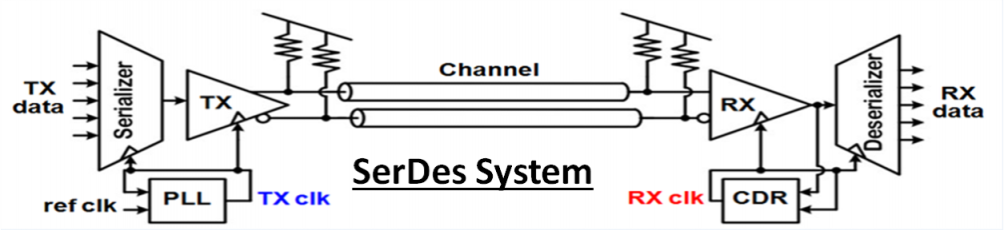

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses the use of multi-core CPUs to significantly reduce PAM4 system simulation time required for a Channel Simulation to achieve accurate BER results… Continue Reading

Monthly Archives: April 2019

Channel Simulation NRZ System MultiCore Tests

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses the use of multi-core CPUs to significantly reduce NRZ system simulation time required for a Channel Simulation to achieve accurate BER results… Continue Reading

Channel Simulation MultiCore Calibration Tests

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses validation of the use of multi-core CPUs to significantly reduce the simulation time required for a Channel Simulation to achieve accurate BER… Continue Reading

Channel Simulation BER Extrapolation

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses BER extrapolation to achieve BER metrics down to 1.0e-16 and lower in Channel Simulations. See the full article: Channel_Simulation_BER_Extrapolation.pdf About John Baprawski… Continue Reading