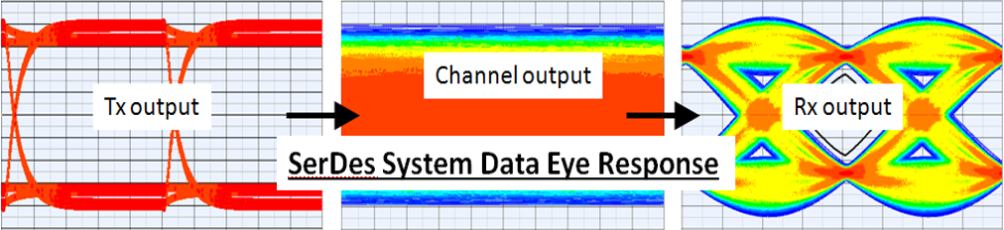

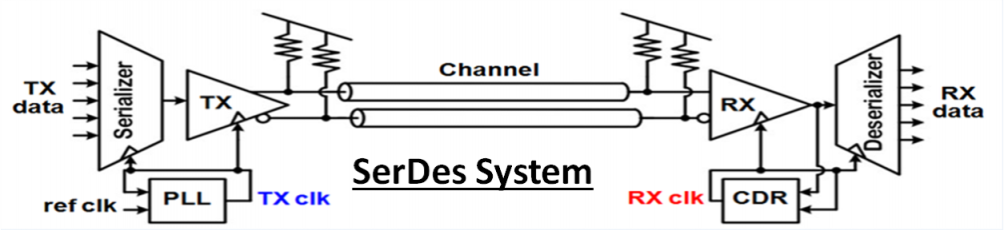

High Speed Digital (HSD) transmit (Tx) and receive (Rx) circuits are modelled as SerDes systems using a channel simulator. Many channel simulators model S-parameter based channels with impulse responses with excessive high frequency aliasing. This paper first gives an overview of high frequency aliasing issues in context with industry standards compliance testing, SerDes systems examples… Continue Reading

Zero Cost SerDes System Channel Simulation

High Speed Digital (HSD) transmit (Tx) and receive (Rx) circuits must be converted by signal integrity engineers to IBIS-AMI models per the IBIS standard to be used in SerDes Channel simulators to evaluate their system margins. This paper first gives an overview of modeling SerDes systems in a channel simulator, introduces the zero-cost tools available… Continue Reading

Overcoming Signal Integrity Channel Modeling Issues

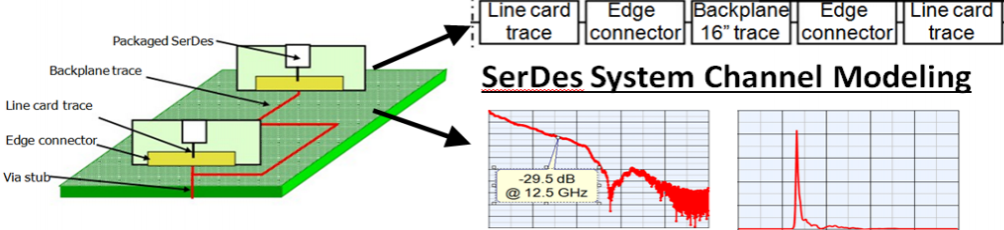

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. S-parameters are used to describe the frequency behavior of a SerDes system channel and are measured on actual hardware or simulated in a frequency domain simulator. This article discusses the issues encountered when using S-parameter files to represent the channel in a… Continue Reading

Automated E-O-E IBIS-AMI Modeling with Reflex Photonics and NXP

Electrical-Optical-Electrical (EOE) systems typically represent repeaters and must be converted to IBIS-AMI models to be used in SerDes Channel Simulators. Today, the IBIS AMI modeling process has matured so that the process can be automated with data collected with S-parameters or time domain waveforms or optical instruments. This paper with Reflex Photonics and NXP proposes… Continue Reading

SerDes Channel Impulse Modeling with Maxim

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In Channel Simulation for such systems, the channel is typically represented with S-parameter which have to be converted to their time domain impulse response equivalent. This paper discussed channel impulse modeling problems encountered by Maxim Intergated and solutions provided by SerDesDesign.com. See… Continue Reading

Keysight 2020 Tokyo Forum – Automated IBIS-AMI Modeling

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In Channel Simulation for such systems, transmit (Tx) and receive (Rx) circuits must exist as IBIS-AMI models. Advanced automated model generation using the SerDesDesign library in the Keysight SystemVue product is discussed in this paper. See the full article: Keysight 2020 Tokyo… Continue Reading

Channel Simulation PAM4 System MultiCore Tests

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses the use of multi-core CPUs to significantly reduce PAM4 system simulation time required for a Channel Simulation to achieve accurate BER results… Continue Reading

Channel Simulation NRZ System MultiCore Tests

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses the use of multi-core CPUs to significantly reduce NRZ system simulation time required for a Channel Simulation to achieve accurate BER results… Continue Reading

Channel Simulation MultiCore Calibration Tests

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses validation of the use of multi-core CPUs to significantly reduce the simulation time required for a Channel Simulation to achieve accurate BER… Continue Reading

Channel Simulation BER Extrapolation

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a Channel Simulator is used to simulate SerDes systems based on the IBIS-AMI standard. This paper discusses BER extrapolation to achieve BER metrics down to 1.0e-16 and lower in Channel Simulations. See the full article: Channel_Simulation_BER_Extrapolation.pdf About John Baprawski… Continue Reading