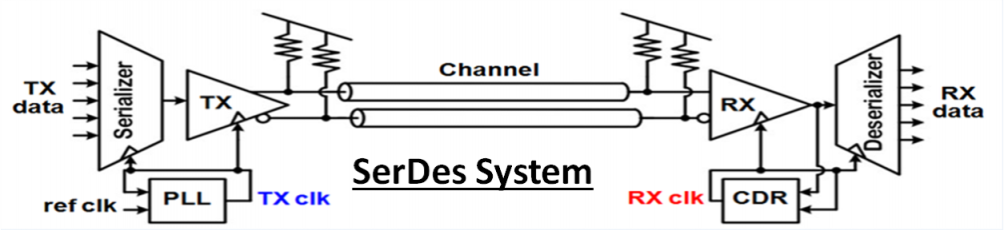

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a receiver (Rx) circuit often needs to be modeled for use in a SerDes system Channel Simulator based on the IBIS-AMI standard. This paper discussed techniques for extracting modeling data for a Rx continuous time linear equalizer (CTLE) circuit.… Continue Reading

Extracting Modeling Data for a Tx FFE Circuit

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a transmit (Tx) circuit often needs to be modeled for use in a SerDes system Channel Simulator based on the IBIS-AMI standard. This paper discusses techniques for extracting modeling data for a Tx feed-forward equalizer (FFE) circuit. See the… Continue Reading

SerDes Channel Impulse Modeling with Signal Metrics

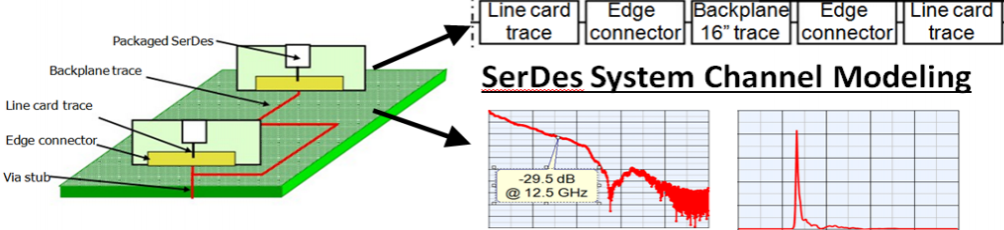

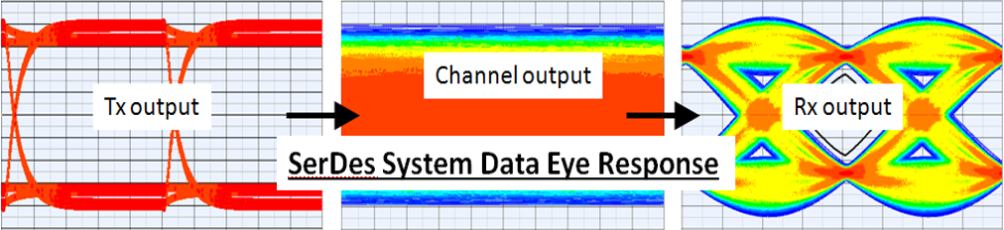

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a lossy differential channel exists between the transmitter (Tx) circuit and the receiver (Rx) circuit. SerDes system are typically analyzed in a Channel Simulator. The channel is typically represented using S-Parameters. This paper was created with Signal Metrics LLC… Continue Reading

SerDes Channel Impulse Modeling with Rambus

High speed digital (HSD) integrated circuits (ICs) are used in Serializer/Deserializer (SerDes) systems. In such systems, a lossy differential channel exists between the transmitter (Tx) circuit and the receiver (Rx) circuit. SerDes system are typically analyzed in a Channel Simulator. The channel is typically represented using S-Parameters. This paper was created with Rambus Inc. during… Continue Reading

A New Method for Developing IBIS-AMI Models with Xilinx

High speed digital (HSD) serial-deserializer (SerDes) system channel simulation is critical for SerDes system design and validation. The simulation must run fast while achieving adequate accuracy. Today’s SerDes system vendors require HSD IBIS-AMI (Input/Output Buffer Information – Algorithmic Modeling Interface) models long before silicon is available. To meet the demand, HSD silicon vendors desire an… Continue Reading

Statistical Model Development for High Speed SerDes with LSI

IBIS Algorithmic Modeling Interface (IBIS-AMI) defines two approaches to SerDes modeling and simulation flow: time domain or bit-by-bit simulation for nonlinear and/or time variant (NLTV) model and statistical simulation for linear and time invariant (LTI) model. Statistical simulation has advantages of faster simulation speed and arbitrary low BER floor under linear model assumption. However, the… Continue Reading