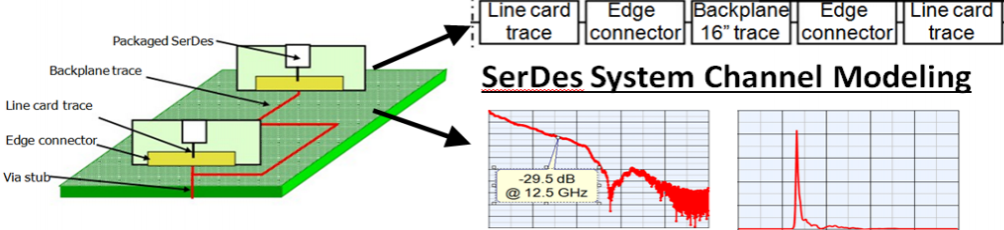

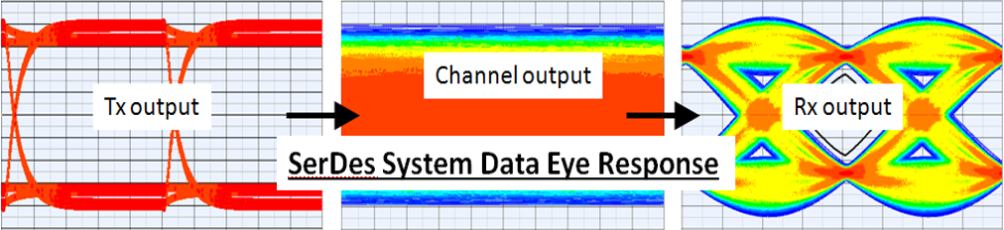

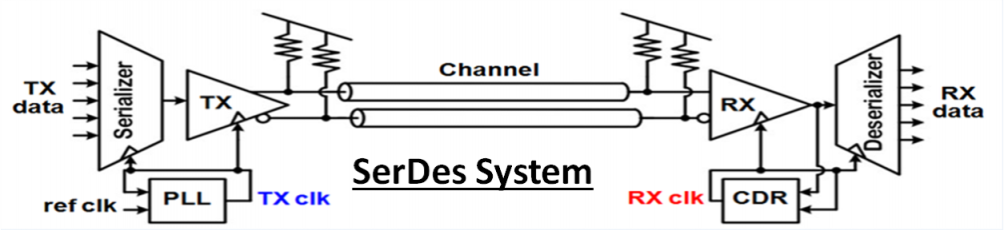

High speed digital (HSD) serial-deserializer (SerDes) system channel simulation is critical for SerDes system design and validation. The simulation must run fast while achieving adequate accuracy. Today’s SerDes system vendors require HSD IBIS-AMI (Input/Output Buffer Information – Algorithmic Modeling Interface) models long before silicon is available. To meet the demand, HSD silicon vendors desire an effective process for generating IBIS-AMI models efficiently and reliably.

This paper with Xilinx Inc. was presented at DesignCon 2015 and proposes a new methodology for AMI model development. Included are discussion of the challenges facing the IBIS-AMI model development, engineering trade-offs needed, modeling methodology and an application on a Xilinx developed HSD IC. The methodology was proven to have shortened the Xilinx development cycle over the previously used method for a 20nm 32Gbps SerDes IC. The developed IBIS-AMI model is tested across multiple EDA platforms. Detailed modeling techniques for accuracy and speed improvement are discussed throughout the paper.

See the full paper: A New Method for Developing IBIS-AMI Models PDF

See the associated PowerPoint: A New Method for Developing IBIS-AMI Models PPTX

About John Baprawski

Hi. I am John Baprawski. I have been a successful electronic system design engineer in the communications and radar product development industries for over 30 years and I can help you meet your product design objectives.

Sorry, comments are closed for this post.